- 이 문서는 삼성전자의 기술 자산으로 승인자만이 사용할 수 있습니다 -

- This Document can not be used without Samsung's authorization -

### 4-1. General spec

#### Tools used for repairing the product

- · System Diagnostics Disk

- · MS-DOS Booting Disk

- · System Diagnostics Card

- Screwdrivers (+,-)

- Tweezers

- Multi-meter

- Oscilloscope

- · Logic Analyzer

#### Replaceable unit (FRU: Field Replaceable Unit)

- DDR2 RAM Module

- 2.5" SATA HDD

- ODD Super multi Dual layer drive or DVD Combo Drive or Etc.

- · Wireless LAN Module

- · Bluetooth Module (Option)

- · MDC Module (Option)

- Key Board

- System Fan

- Touch Pad

- LCD Panel

- LCD Inverter

- Main Board

- Express Card Frame

- Harness Cable-Touchpad FFC, MDC Cable (On board), MDC Cable (To RJ11), Bluetooth Cable, LCD Cable, Wireless LAN Antenna 3 types, Camera cable, DMB Antenna

- 이 문서는 삼성전자의 기술 자산으로 승인자만이 사용할 수 있습니다 -

- This Document can not be used without Samsung's authorization -

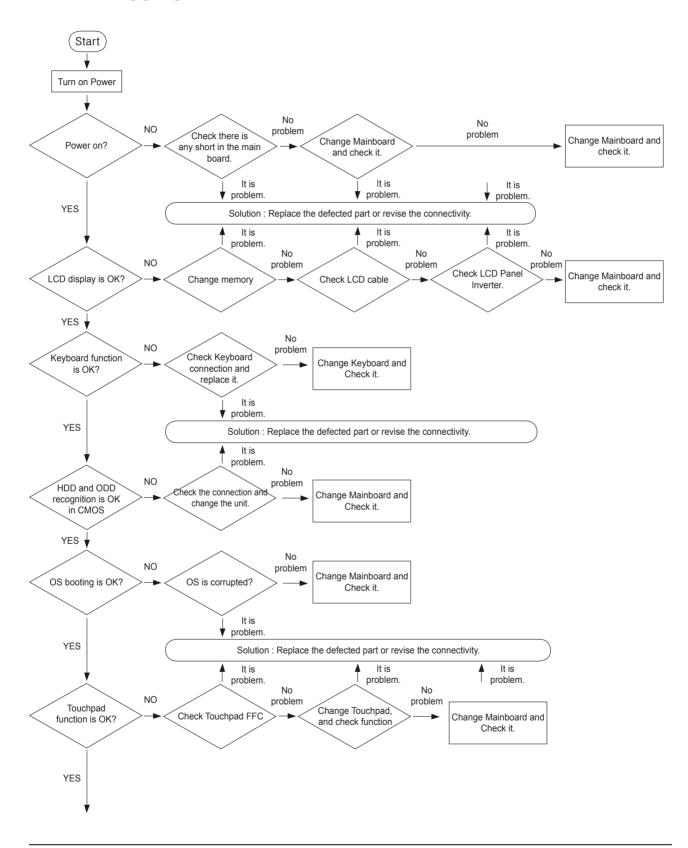

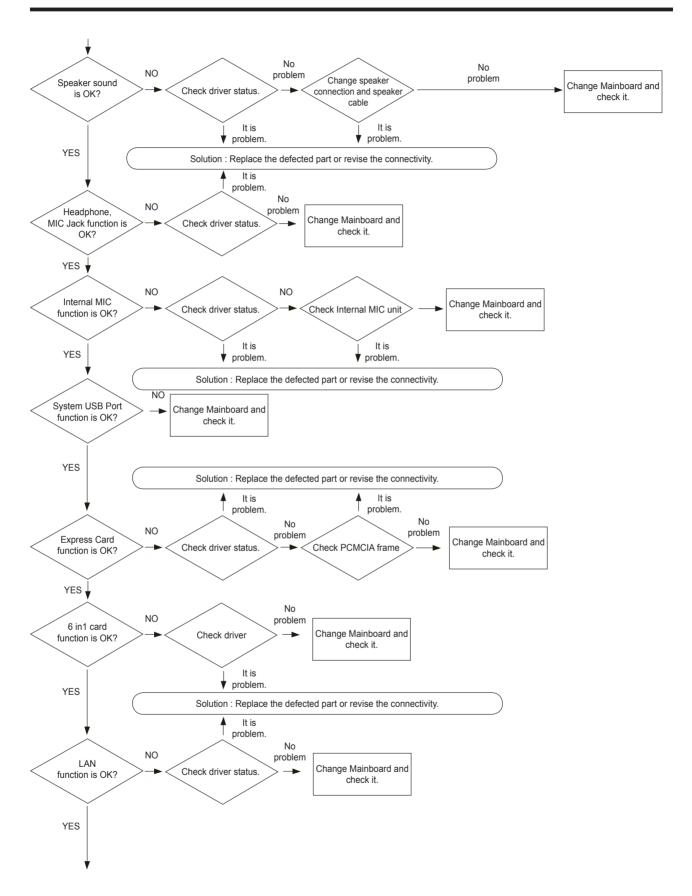

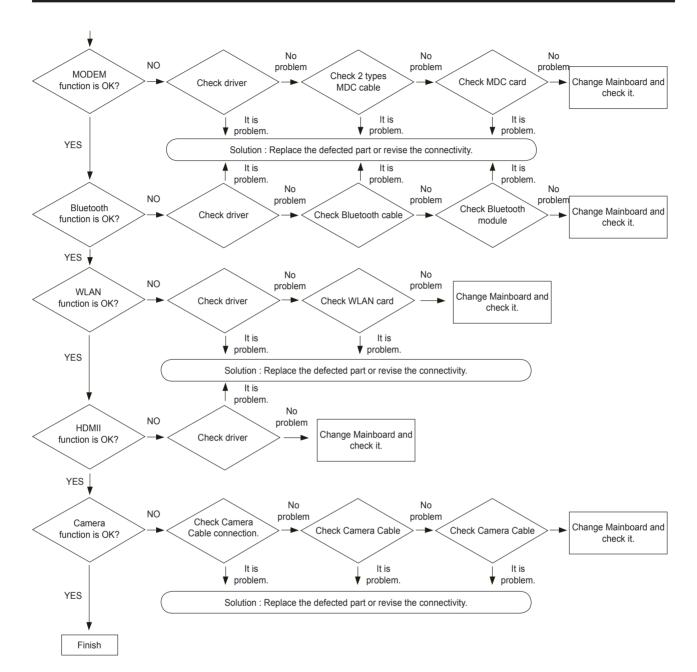

### 4-2. Debugging Flow Chart

- 이 문서는 삼성전자의 기술 자산으로 승인자만이 사용할 수 있습니다 -

- This Document can not be used without Samsung's authorization -

- 이 문서는 삼성전자의 기술 자산으로 승인자만이 사용할 수 있습니다 -

- This Document can not be used without Samsung's authorization -

- 이 문서는 삼성전자의 기술 자산으로 승인자만이 사용할 수 있습니다 -

- This Document can not be used without Samsung's authorization -

## 4-3. System Diagnosis

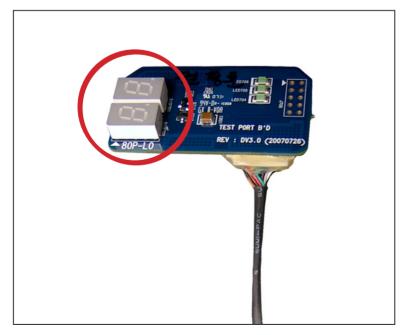

### **System Diagnostics Card**

The Diagnostics Card shows the system operations during the POST (Power On Self Test) in a 2 digit hexadecimal number by connecting the cable to the 10 pin connector below the PCMCIA slot after separating the Top part. The card is used to evaluate the reason for the malfunction without disassembling the system when the system malfunctions and to test if the system operates normally after replacing a defective FRU.

### **Chipset POST Codes Table**

| POST Code | Function                                                                    | Phase | Component   |

|-----------|-----------------------------------------------------------------------------|-------|-------------|

| 0xA0      | MRC Entry                                                                   | PEI   | chipset/MRC |

| 0x01      | Enable MCHBAR                                                               | PEI   | chipset/MRC |

| 0x02      | Check ME existence                                                          | PEI   | chipset/MRC |

| 0x03      | Check for DRAM initialization interrupt and reset fail                      | PEI   | chipset/MRC |

| 0x04      | Determine the system Memory type based on first populated socket            | PEI   | chipset/MRC |

| 0x05      | Verify all DIMMs are DDR2 and SO-DIMMS, which are unbuffered                | PEI   | chipset/MRC |

| 0x06      | Verify all DIMMs are Non-ECC                                                | PEI   | chipset/MRC |

| 0x07      | Verify all DIMMs are single or double sided and not mixed                   | PEI   | chipset/MRC |

| 0x08      | Verify all DIMMs are x8 or x16 width                                        | PEI   | chipset/MRC |

| 0x09      | Calculate number of Row and Column bits                                     | PEI   | chipset/MRC |

| 0x10      | Calculate number of banks for each DIMM                                     | PEI   | chipset/MRC |

| 0x11      | Determine raw card type                                                     | PEI   | chipset/MRC |

| 0x12      | Find a common CAS latency between the DIMMS and the MCH                     | PEI   | chipset/MRC |

| 0x13      | Determine the memory frequency and CAS latency to program                   | PEI   | chipset/MRC |

| 0x14      | Determine the smallest common timing value for all DIMMS                    | PEI   | chipset/MRC |

| 0x17      | Power management resume                                                     | PEI   | chipset/MRC |

| 0x18      | Program DRAM type (DDR2/DDR3) and Power up sequence                         | PEI   | chipset/MRC |

| 0x19      | Program the correct system memory frequency                                 | PEI   | chipset/MRC |

| 0x20      | Program the correct Graphics memory frequency                               | PEI   | chipset/MRC |

| 0x21      | Early DRC initialization                                                    | PEI   | chipset/MRC |

| 0x22      | Program the DRAM Row Attributes and DRAM Row Boundary registers PRE JEDEC.b | PEI   | chipset/MRC |

| 0x23      | Program the RCOMP SRAM registers                                            | PEI   | chipset/MRC |

| 0x24      | Program DRAM type (DDR2/DDR3) and Power up sequence                         | PEI   | chipset/MRC |

| 0x25      | Program the DRAM Timing                                                     | PEI   | chipset/MRC |

| 0x26      | Program the DRAM Bank Architecture register                                 | PEI   | chipset/MRC |

| 0x27      | Enable all clocks on populated rows                                         | PEI   | chipset/MRC |

| 0x28      | Program MCH ODT                                                             | PEI   | chipset/MRC |

| 0x29      | Program tRD                                                                 | PEI   | chipset/MRC |

| 0x30      | Miscellaneous Pre JEDEC steps                                               | PEI   | chipset/MRC |

| 0x31      | Program clock crossing registers                                            | PEI   | chipset/MRC |

| 0x32      | Program the Egress port timings                                             | PEI   | chipset/MRC |

| 0x33      | Program the Memory IO registers                                             | PEI   | chipset/MRC |

| 0x34      | Perform steps required before JEDEC                                         | PEI   | chipset/MRC |

| 0x35      | Perform JEDEC memory initialization for all memory rows                     | PEI   | chipset/MRC |

| 0x36      | Setup DRAM control register for normal operation and enable                 | PEI   | chipset/MRC |

- 이 문서는 삼성전자의 기술 자산으로 승인자만이 사용할 수 있습니다 -

- This Document can not be used without Samsung's authorization -

| POST Code | Function                                                                                                    | Phase       | Component   |  |

|-----------|-------------------------------------------------------------------------------------------------------------|-------------|-------------|--|

| 0x37      | Do ZQ calibration for DDR3                                                                                  | PEI         | chipset/MRC |  |

| 0x38      | Perform final Dra/Drb programming, Set the mode of operation for the memory channels                        | PEI         | chipset/MRC |  |

| 0x39      | Set Enhanced addressing mode for each channel                                                               | PEI         | chipset/MRC |  |

| 0x40      | Perform steps required after JEDEC init                                                                     | PEI         | chipset/MRC |  |

| 0x41      | Program the receive enable reference timing control register                                                | chipset/MRC |             |  |

| 0x42      | Post receive enable initialization                                                                          | PEI         | chipset/MRC |  |

| 0x43      | Enable sense amps. Reset read/write DQS pointers                                                            | PEI         | chipset/MRC |  |

| 0x44      | Perform ME steps                                                                                            | PEI         | chipset/MRC |  |

| 0x45      | Clear DRAM initialization bit in the ICH.                                                                   | PEI         | chipset/MRC |  |

| 0x46      | Program Thermal Management                                                                                  | PEI         | chipset/MRC |  |

| 0x47      | Program TS on DIMM                                                                                          | PEI         | chipset/MRC |  |

| 0x48      | Program TS on Board                                                                                         | PEI         | chipset/MRC |  |

| 0xAF      | Exit MRC                                                                                                    | PEI         | chipset/MRC |  |

| 0xE0      | #define MEM_ERR_BAD_DIMM (S11)                                                                              | PEI         | chipset/MRC |  |

| 0xE1      | #define MEM_ERR_ECC_DIMM (S06)                                                                              | PEI         | chipset/MRC |  |

| 0xE2      | #define MEM_ERR_SIDES (S07)                                                                                 | PEI         | chipset/MRC |  |

| 0xE3      | #define MEM_ERR_WIDTH (S08, S10)                                                                            | PEI         |             |  |

| 0xE4      | #define MEM_ERR_TRFC (FindTrasTrpTrcd)                                                                      | PEI         | chipset/MRC |  |

| 0xE5      | #define MEM_ERR_CAS_LATENCY (S12, S13)                                                                      | PEI         | chipset/MRC |  |

| 0xE6      | #define MEM_ERR_REFRESH (ProgDrt )                                                                          | PEI         | chipset/MRC |  |

| 0xE7      | #define MEM_ERR_BL8 (S14) PEI                                                                               |             | chipset/MRC |  |

| 0xE9      | #define MEM_ERR_FREQUENCY (findTCLTacTClk, S13, S12, ProgramGraphicsFrequency, ProgMchOdt, GetPlatformData) | PEI         | chipset/MRC |  |

| 0xEA      | #define MEM_ERR_SIZE (S14)                                                                                  | PEI         | chipset/MRC |  |

| 0xEC      | #define MEM_ERR_TRAS (FindTrasTrpTrcd)                                                                      | PEI         | chipset/MRC |  |

| 0xED      | #define MEM_ERR_TRP (FindTrasTrpTrcd)                                                                       | PEI         | chipset/MRC |  |

| 0xEE      | #define MEM_ERR_TRCD (FindTrasTrpTrcd)                                                                      | PEI         | chipset/MRC |  |

| 0xEF      | #define MEM_ERR_TWR (FindTrasTrpTrcd)                                                                       | PEI         | chipset/MRC |  |

| 0xF0      | #define MEM_ERR_RCVEN_FINDLOW (CalibrateRcvenForGroup)                                                      | PEI         | chipset/MRC |  |

| 0xF1      | #define MEM_ERR_RCVEN_FINDEDGE (CalibrateRcvenForGroup)                                                     | PEI         | chipset/MRC |  |

| 0xF2      | #define MEM_ERR_RCVEN_FINDPREAMBLE (CalibrateRcvenForGroup)                                                 | PEI         | chipset/MRC |  |

| 0xF6      | #define MEM_ERR_RCVEN_PREAMBLEEDGE (CalibrateRcvenForGroup)                                                 | PEI         | chipset/MRC |  |

| 0xF3      | #define MEM_ERR_RCVEN_FINDCENTER (CalibrateRcvenForGroup)                                                   | PEI         | chipset/MRC |  |

| 0xF4      | #define MEM_ERR_TYPE (S11, S04)                                                                             | PEI         | chipset/MRC |  |

| 0xF5      | #define MEM_ERR_RAWCARD (S11)                                                                               | PEI         | chipset/MRC |  |

| 0xFA      | #define MEM_ERR_SFF (ProgWrioDII)                                                                           | PEI         | chipset/MRC |  |

| 0xFB      | #define MEM_ERR_THERMAL (ProgramThrottling)                                                                 | PEI         | chipset/MRC |  |

| 0xA0xx    | Launch BIOS ACMSclean                                                                                       | PEI         | chipset/TXT |  |

| 0xA4xx    | Launch BIOS ACMScheck                                                                                       | PEI         | chipset/TXT |  |

| 0xE5      | Wait for ME ready                                                                                           | DXE         | HECI/iAMT   |  |

| 0xE6      | ME Ready                                                                                                    | DXE         | HECI/iAMT   |  |

- 이 문서는 삼성전자의 기술 자산으로 승인자만이 사용할 수 있습니다 -

- This Document can not be used without Samsung's authorization -

### **Core POST Codes Table**

| POST Code | Function                                                             | Phase           | Component |

|-----------|----------------------------------------------------------------------|-----------------|-----------|

| 0x00      | Early Microcode update for CAR                                       | CEI / SEC       | Core      |

| 0x01      | Enable CAR                                                           | CEI / SEC       | Core      |

| 0x02      | CAR Done, initial stack                                              | CEI / SEC       | Core      |

| 0xEE      | unknown CPU ID to load uCode                                         | CEI / SEC       | CPU       |

| 0xEF      | unknown DT CPU to load uCode                                         | CEI / SEC       | CPU       |

| 0xnn      | File count found in a volume                                         | PEI             | Core      |

| 0x11      | Debug Test driver for debug test PPI 1 (If install debugTest driver) | PEI             | Core      |

| 0x22      | Debug Test driver for debug test PPI 2 (If install debugTest driver) | PEI             | Core      |

| 0x33      | Debug Test driver for debug test PPI 3 (If install debugTest driver) | PEI             | Core      |

| 0x44      | Entry point of loadfile                                              | PEI             | Core      |

| 0x88      | Entry point of apMuLoader                                            | PEI             | Core      |

| 0x80      | A PEIM found                                                         | PEI             | Core      |

| 0x82      | PEIM not dispatched yet                                              | PEI             | Core      |

| 0x84      | PEIM satisfies depex                                                 | PEI             | Core      |

| 0x86      | Image loaded but fail on security                                    | PEI             | Core      |

| 0x88      | Executing a PEIM                                                     | PEI             | Core      |

| 0x8A      | Processing notify event for newly installed PPI                      | PEI             | Core      |

| 0x8C      | Handing off to next phase (DXE)                                      | PEI             | Core      |

| 0x8F      | Fail to hand off to next phase, system halt                          | PEI             | Core      |

| 0x90      | All.PEIM.dispatched!.Going.to.Dxelpl.                                | PEI             | Core      |

| 0xCC      | AP Micro-code update                                                 | PEI             | Core      |

| 0x20      | S3 resume entry                                                      | S3 resume       | Core      |

| 0x21      | Start running Boot-time bootscripts                                  | S3 resume       | Core      |

| 0x22      | Start running Run-time bootscripts                                   | S3 resume       | Core      |

| 0x23      | End of S3 resume, jump back to Waking vector                         | S3 resume       | Core      |

| 0x80      | Initialize the chipset                                               | Crisis Recovery | Core      |

| 0x81      | Initialize the bridge                                                | Crisis Recovery | Core      |

| 0x82      | Initialize the CPU                                                   | Crisis Recovery | Core      |

| 0x89      | Set Huge Segment                                                     | Crisis Recovery | Core      |

| 0x83      | Initialize system timer                                              | Crisis Recovery | Core      |

| 0x84      | Initialize system I/O                                                | Crisis Recovery | Core      |

| 0x88      | Initialize Multi Processor                                           | Crisis Recovery | Core      |

| 0x8A      | Initialize OEM special code                                          | Crisis Recovery | Core      |

| 0x8B      | Initialize PIC and DMA                                               | Crisis Recovery | Core      |

| 0x8C      | Initialize Memory type                                               | Crisis Recovery | Core      |

| 0x8D      | Initialize Memory size                                               | Crisis Recovery | Core      |

| 0x8F      | Initialize SMM                                                       | Crisis Recovery | Core      |

| 0x90      | System memory test                                                   | Crisis Recovery | Core      |

| 0x91      | Initialize interrupt vectors                                         | Crisis Recovery | Core      |

| 0x92      | Initialize Run Time Clock                                            | Crisis Recovery | Core      |

| 0x99      | Initialize security                                                  | Crisis Recovery | Core      |

| 0x93      | Initialize video                                                     | Crisis Recovery | Core      |

| 0x94      | Output one beep                                                      | Crisis Recovery | Core      |

| 0x98      | USB Initialization                                                   | Crisis Recovery | Core      |

- 이 문서는 삼성전자의 기술 자산으로 승인자만이 사용할 수 있습니다 -

- This Document can not be used without Samsung's authorization -

| POST Code | Function                                                                   | Phase           | Component |

|-----------|----------------------------------------------------------------------------|-----------------|-----------|

| 0x95      | Initialize the installed boot devices                                      | Crisis Recovery | Core      |

| 0x96      | Clear Huge segment                                                         | Crisis Recovery | Core      |

| 0x97      | Boot Crisis Disk                                                           | Crisis Recovery | Core      |

| 0x20      | DXE starts                                                                 | DXE             | Core      |

| 0x30      | BIOSPSM                                                                    | DXE             | Core      |

| 0x02      | BIOSBlockIO                                                                | DXE             | Core      |

| 0x00      | BIOSPSM Exception Handler - Divide error                                   | BIOSPSM         | Core      |

| 0x38      | Cannot locate LegacyRegion DXE                                             | BIOSPSM         | Core      |

| 0xB1      | ACPISupport driver Installed                                               | DXE             | Core      |

| 0xE0      | BDS Entry                                                                  | DXE             | Core      |

| 0x07      | IA32 variable driver entry                                                 | DXE             | Core      |

| 0x0D      | conspliter driver entry                                                    | DXE             | Core      |

| 0x10      | partition driver entry                                                     | DXE             | Core      |

| 0x49      | pciRootBridge driver entry                                                 | DXE             | Core      |

| 0xC6      | pciBusDriver entry                                                         | DXE             | Core      |

| 0xE0      | Go to legacy BIOS or BDS Entry Point                                       | DXE             | Core      |

| 0x90      | Start Image                                                                | DXE             | Core      |

| 0x90      | Start Image Successfully                                                   | DXE             | Core      |

| 0x90      | Start Image Failed                                                         | DXE             | Core      |

| 0x33      | Debug Test driver for debug test PPI 1                                     | DXE             | Core      |

| 0x22      | Debug Test driver for debug test PPI 2                                     | PEI             | Core      |

| 0x11      | Debug Test driver for debug test PPI 3                                     | PEI             | Core      |

| 0x02      | Invalid event # for measuring Separator Event                              | PEI             | TCG       |

| 0x02      | Invalid event # for measuring Separator Event                              | PEI             | TCG       |

| 0x02      | PCR Index over limit (PCR > 23)                                            | PEI             | TCG       |

| 0x02      | TCG copy memory failed                                                     | PEI             | TCG       |

| 0x09      | TCG log event failed                                                       | PEI             | TCG       |

| 0x09      | Setup event log failed                                                     | PEI             | TCG       |

| 0x12      | TIS set active locality failed                                             | PEI             | TCG       |

| 0x12      | TIS relinquish active locality failed                                      | DXE             | TCG       |

| 0x12      | TIS wait command ready failed (prepare to send)                            | DXE             | TCG       |

| 0x12      | TIS abort 'send 'command due to timeout                                    | DXE             | TCG       |

| 0x12      | TIS abort 'sendAndGo 'command due to timeout                               | DXE             | TCG       |

| 0x04      | TIS wait bit set failed before send last byte                              | DXE             | TCG       |

| 0x12      | TIS abort command due to timeout before send last byte                     | DXE             | TCG       |

| 0x04      | TIS wait bit clear failed when sending last byte                           | DXE             | TCG       |

| 0x22      | TCG Physical Presence execution                                            | DXE             | TCG       |

| 0xB1      | TCG DXE common pass through                                                | DXE             | TCG       |

| 0xE3      | First Legacy BIOS Task table for legacy reset                              | LBT             | Core      |

| 0x20      | Verify that DRAM refresh is operating by polling the refresh bit in PORTB. | LBT             | Core      |

| 0xDA      | Dummy PCIE Init entry, now handled by driver                               | LBT             | Core      |

| 0x29      | PMM (POST Memory Manager) init                                             | LBT             | Core      |

| 0xE5      | WHEA init                                                                  | LBT             | Core      |

| 0x33      | PDM (Post Dispatcher Manager) init                                         | LBT             | Core      |

| 0x01      | IPMI init                                                                  | LBT             | Core      |

- 이 문서는 삼성전자의 기술 자산으로 승인자만이 사용할 수 있습니다 -

- This Document can not be used without Samsung's authorization -

| POST Code | Function                                                                                                                                                                                                                                                                                                 | Phase | Component |

|-----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|-----------|

| 0xD8      | ASF Init                                                                                                                                                                                                                                                                                                 | LBT   | Core      |

| 0x09      | Set in-POST flag in CMOS that indicates we are in POST. If this bit is not cleared by postClearBootFlagJ (AEh), the TrustedCore on next bo ot determines that the current configuration caused POST to fail and u ses default values for configuration.  Clear the                                       | LBT   | Core      |

| 0x2B      | Enhanced CMOS init                                                                                                                                                                                                                                                                                       | LBT   | Core      |

| 0xE0      | EFI Variable Init                                                                                                                                                                                                                                                                                        | LBT   | Core      |

| 0xC1      | PEM (Post Error Manager) init                                                                                                                                                                                                                                                                            | LBT   | Core      |

| 0x3B      | Debug Service Init (ROM Polit)                                                                                                                                                                                                                                                                           | LBT   | Core      |

| 0xDC      | POST Update Error                                                                                                                                                                                                                                                                                        | LBT   | Core      |

| 0x3A      | Autosize external cache and program cache size for enabling later in POST.                                                                                                                                                                                                                               | LBT   | Core      |

| 0x0B      | Enable CPU cache. Set bits in cmos related to cache.                                                                                                                                                                                                                                                     | LBT   | Core      |

| 0x0F      | Enable the local bus IDE as primary or secondary depending on other drives detected.                                                                                                                                                                                                                     | LBT   | Core      |

| 0x10      | Initialize Power Management.                                                                                                                                                                                                                                                                             | LBT   | Core      |

| 0x14      | Verify that the 8742 keyboard controller is responding. Send a self-<br>test command to the 8742 and wait for results. Also read the switch<br>inputs from the 8742 and write the keyboard controller command byte.                                                                                      | LBT   | Core      |

| 0x1A      | Initialize DMA command register with these settings:  1. Memory to memory disabled  2. Channel 0 hold address disabled  3. Controller enabled  4. Normal timing  5. Fixed priority  6. Late write selection  7. DREQ sense active  8. DACK sense active low. Initialize                                  | LBT   | Core      |

| 0x22      | Reset the keyboard.                                                                                                                                                                                                                                                                                      | LBT   | Core      |

| 0x40      | Test A20 line                                                                                                                                                                                                                                                                                            | LBT   | Core      |

| 0x67      | Quick initialization of all Application Processors in a multi-processor system                                                                                                                                                                                                                           | LBT   | Core      |

| 0x32      | Compute CPU speed.                                                                                                                                                                                                                                                                                       | LBT   | Core      |

| 0x69      | Initialize the handler for SMM.                                                                                                                                                                                                                                                                          | LBT   | Core      |

| 0x6B      | If CMOS is bad, load Custom Defaults from flash into CMOS. If successful, reboot.                                                                                                                                                                                                                        | LBT   | Core      |

| 0x3C      | If CMOS is valid, load chipset registers with values from CMOS, otherwise load defaults and display Setup prompt. If Auto Configuration is enabled, always load the chipset registers with the Setup defaults (Rel 6.0).                                                                                 | LBT   | Core      |

| 0x3D      | Load alternate registers with CMOS values                                                                                                                                                                                                                                                                | LBT   | Core      |

| 0x42      | Initialize interrupt vectors 0 thru 77h                                                                                                                                                                                                                                                                  | LBT   | Core      |

| 0x46      | Verify the ROM copyright notice                                                                                                                                                                                                                                                                          | LBT   | Core      |

| 0x45      | Initialize all motherboard devices.                                                                                                                                                                                                                                                                      | LBT   | Core      |

| 0x49      | <ol> <li>Size the PCI bus topology and set bridge bus numbers.</li> <li>Set the system max bus number.</li> <li>Write a 0 to the command register of every PCI device.</li> <li>Write a 0 to all 6 base registers in every PCI device.</li> <li>Write a -1 to the status register of every PC</li> </ol> | LBT   | Core      |

| 0xC6      | Initialize note dock                                                                                                                                                                                                                                                                                     | LBT   | Core      |

| 0xC5      | PnPnd dual CMOS (optional)                                                                                                                                                                                                                                                                               | LBT   | Core      |

- 이 문서는 삼성전자의 기술 자산으로 승인자만이 사용할 수 있습니다 -

- This Document can not be used without Samsung's authorization -

| POST Code | Function                                                                                                                                                                                                                                                        | Phase | Component |

|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|-----------|

| 0x48      | Verify that the equipment specified in the CMOS matches the hardware currently installed. If the monitor type is set to 00 then a video ROM must exist. If the monitor type is 1 or 2 set the video switch to CGA. If monitor type 3, set the video switch to m | LBT   | Core      |

| 0xD1      | Initialize BIOS stack                                                                                                                                                                                                                                           | LBT   | Core      |

| 0xD3      | Setup E820h and WAD memory map                                                                                                                                                                                                                                  | LBT   | Core      |

| 0x24      | Set segment-register addressability to 4 GB                                                                                                                                                                                                                     | LBT   | Core      |

| 0xCC      | Redirect Int 10h to enable target board to use a remote serial video (PICO BIOS).                                                                                                                                                                               | LBT   | Core      |

| 0x8A      | Initialize Extended BIOS Data Area and initialize the mouse.                                                                                                                                                                                                    | LBT   | Core      |

| 0x9D      | Initialize Security Engine.                                                                                                                                                                                                                                     | LBT   | Core      |

| 0x55      | USB Initialization                                                                                                                                                                                                                                              | LBT   | Core      |

| 0x52      | Verify keyboard reset.                                                                                                                                                                                                                                          | LBT   | Core      |

| 0x54      | Initialize keystroke clicker if enabled in Setup.                                                                                                                                                                                                               | LBT   | Core      |

| 0x76      | Check status bits for keyboard-related failures. Display error messages on the screen.                                                                                                                                                                          | LBT   | Core      |

| 0x4A      | Initialize all video adapters in system                                                                                                                                                                                                                         | LBT   | Core      |

| 0x4C      | Shadow video BIOS ROM if specified by Setup, and CMOS is valid and the previous boot was OK.                                                                                                                                                                    | LBT   | Core      |

| 0x59      | Register POST Display Services, fonts, and languages with the POST Dispatch Manager.                                                                                                                                                                            | LBT   | Core      |

| 0x57      | Initialize 1394 Firewire                                                                                                                                                                                                                                        | LBT   | Core      |

| 0xD6      | Initialize PC card                                                                                                                                                                                                                                              | LBT   | Core      |

| 0x58      | Test for unexpected interrupts. First do an STI for hot interrupts. Secondly, test the NMI for an unexpected interrupt. Thirdly, enable the parity checkers and read from memory, checking for an unexpected interrupt.                                         | LBT   | Core      |

| 0x3F      | ROMPolit memory init                                                                                                                                                                                                                                            | LBT   | Core      |

| 0xC4      | Install the IRQ vectors (Sever Hotkey)                                                                                                                                                                                                                          | LBT   | Core      |

| 0x7C      | Initialize the hardware interrupt vectors from 08 to 0F and from 70h to 77H. Also set the interrupt vectors from 60h to 66H to zero.                                                                                                                            | LBT   | Core      |

| 0x41      | ROM Pilot Init                                                                                                                                                                                                                                                  | LBT   | Core      |

| 0x4B      | Initialize QuietBoot if it is installed. Enable both keyboard and timer interrupts (IRQ0 and IRQ1). If your POST tasks require interrupts off, preserve them with a PUSHF and CLI at the beginning and a POPF at the end. If you change the PIC, preserve the e | LBT   | Core      |

| 0xDE      | Initialize and UNDI ROM (fro remote flash)                                                                                                                                                                                                                      | LBT   | Core      |

| 0xC6      | Initial and install console for UCR                                                                                                                                                                                                                             | LBT   | Core      |

| 0x4E      | Display copyright notice.                                                                                                                                                                                                                                       | LBT   | Core      |

| 0xD4      | Get CPU branding string                                                                                                                                                                                                                                         | LBT   | Core      |

| 0x50      | Display CPU type and speed                                                                                                                                                                                                                                      | LBT   | Core      |

| 0xC9      | pretask before EISA init                                                                                                                                                                                                                                        | LBT   | Core      |

| 0x51      | EISA Init                                                                                                                                                                                                                                                       | LBT   | Core      |

| 0x5A      | Display prompt "Press F2 to enter SETUP"                                                                                                                                                                                                                        | LBT   | Core      |

| 0x5B      | Disable CPU cache.                                                                                                                                                                                                                                              | LBT   | Core      |

| 0x5C      | Test RAM between 512K and 640K.                                                                                                                                                                                                                                 | LBT   | Core      |

| 0x60      | Determine and test the amount of extended memory available.  Determine if memory exists by writing to a few strategic locations and see if the data can be read back. If so, perform an address-line test and a RAM test on the memory. Save the total extended | LBT   | Core      |

- 이 문서는 삼성전자의 기술 자산으로 승인자만이 사용할 수 있습니다 -

- This Document can not be used without Samsung's authorization -

| POST Code | Function                                                                                                                                                                                                                                        | Phase | Component |

|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|-----------|

| 0x62      | The amount of memory available. This test is dependent on the processor, since the test will vary depending on the width of memory (16 or 32 bits). This test will also use A20 as the skew address to prevent corruption of the system memory. | LBT   | Core      |

| 0x64      | Jump to UserPatch1.                                                                                                                                                                                                                             | LBT   | Core      |

| 0x66      | Set cache registers to their CMOS values if CMOS is valid, unless auto configuration is enabled, in which case load cache registers from the Setup default table.                                                                               | LBT   | Core      |

| 0x68      | Enable external cache and CPU cache if present. Configure non-cacheable regions if necessary.                                                                                                                                                   | LBT   | Core      |

| 0x6A      | Display external cache size on the screen if it is non-zero.                                                                                                                                                                                    | LBT   | Core      |

| 0x6C      | Display shadow message                                                                                                                                                                                                                          | LBT   | Core      |

| 0xCA      | post EISA init                                                                                                                                                                                                                                  | LBT   | Core      |

| 0x70      | Check flags in CMOS and in the TrustedCore data area for errors detected during POST. Display error messages on the screen.                                                                                                                     | LBT   | Core      |

| 0x72      | Check status bits to see if configuration problems were detected. If so, display error messages on the screen.                                                                                                                                  | LBT   | Core      |

| 0x4F      | Initialize MultiBoot. Allocate memory for old and new MultiBoot history tables.                                                                                                                                                                 | LBT   | Core      |

| 0xCD      | Reclaim console vector after HW vectors initialized.                                                                                                                                                                                            | LBT   | Core      |

| 0x7D      | Initialize Intelligent System Monitoring.                                                                                                                                                                                                       | LBT   | Core      |

| 0x7E      | The Coprocessor initialization test. Use the floating point instructions to determine if a coprocessor exists instead of the ET bit in CR0.                                                                                                     |       | Core      |

| 0xC1      | Check Boot Type (Server BIOS)                                                                                                                                                                                                                   | LBT   | Core      |

| 0x80      | Disable onboard COM and LPT ports before testing for presence of external I/O devices                                                                                                                                                           | LBT   | Core      |

| 0xCA      | Redirect Int 15h to enable target board to use remote keyboard (PICO BIOS).                                                                                                                                                                     | LBT   | Core      |

| 0x88      | Initialize interrupt controller.                                                                                                                                                                                                                | LBT   | Core      |

| 0x81      | Run late device initialization routines.                                                                                                                                                                                                        | LBT   | Core      |

| 0x87      | Initialize motherboard configurable devices.                                                                                                                                                                                                    | LBT   | Core      |

| 0x85      | Display any ESCD read errors and configure all PnP ISA devices.                                                                                                                                                                                 | LBT   | Core      |

| 0x82      | Test and identify RS232 ports.                                                                                                                                                                                                                  | LBT   | Core      |

| 0x84      | Test and identify parallel ports.                                                                                                                                                                                                               | LBT   | Core      |

| 0x86      | Initialize onboard I/O and BDA according to CMOS and presence of external devices.                                                                                                                                                              | LBT   | Core      |

| 0x83      | Configure Fisk Disk Controller.                                                                                                                                                                                                                 | LBT   | Core      |

| 0xCE      | Initialize digitizer device and display installed message if successful.                                                                                                                                                                        | LBT   | Core      |

| 0x89      | Enable non-maskable interrupts.                                                                                                                                                                                                                 | LBT   | Core      |

| 0x8C      | Initialize both of the floppy disks and display an error message if failure was detected. Check both drives to establish the appropriate diskette types in the TrustedCore data area                                                            |       |           |

| 0xCB      | Redirect Int 13h to Memory Technologies Devices such as ROM, RAM , PCMCIA, and serial disk (PICO BIOS).                                                                                                                                         |       |           |

| 0xCD      | Remap I/O and memory address space for PCMCIA (PICO BIOS).                                                                                                                                                                                      |       |           |

| 0x90      | Initialize hard-disk controller. If the CMOS ram is valid and intact, and fixed disks are defined, call the fixed disk init routine to initialize the fixed disk system and take over the appropriate interrupt vectors.                        |       |           |

| 0x8B      | Setup interrupt vector and present bit in Equipment byte.                                                                                                                                                                                       |       |           |

- 이 문서는 삼성전자의 기술 자산으로 승인자만이 사용할 수 있습니다 -

- This Document can not be used without Samsung's authorization -

| POST Code | Function                                                                                                                                                                                                                                             | Phase | Component |

|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|-----------|

| 0x95      | Check CMOS for CD-ROM drive present     Activate the drive by checking for media present     Check sector 11h (17) for Boot Record Volume Descriptor     Check the boot catalog for validity     Pick a boot entry     Create a Specification Packet | LBT   | Core      |

| 0x92      | Jump to UserPatch2.                                                                                                                                                                                                                                  | LBT   | Core      |

| 0xB6      | If password on boot is enabled, a call is made to Setup to check password. If the user does not enter a valid password, Setup does not return.                                                                                                       | LBT   | Core      |

| 0x98      | Search for option ROMs. Rom scan the area from C800h for a length of BCP_ROM_Scan_Size (or to E000h by default) on every 2K boundary, looking for add on cards that need initialization.                                                             | LBT   | Core      |

| 0x93      | Build the MPTABLE for multi-processor boards                                                                                                                                                                                                         | LBT   | Core      |

| 0xD9      | IPMI late init                                                                                                                                                                                                                                       | LBT   | Core      |

| 0x9C      | Set up Power Management. Initiate power-management state machine.                                                                                                                                                                                    | LBT   | Core      |

| 0xC7      | Late note dock init                                                                                                                                                                                                                                  | LBT   | Core      |

| 0x9E      | Enable hardware interrupts                                                                                                                                                                                                                           | LBT   | Core      |

| 0xA0      | Setup time tick for current date/time                                                                                                                                                                                                                | LBT   | Core      |

| 0xA2      | Setup Numlock indicator. Display a message if key switch is locked.                                                                                                                                                                                  | LBT   | Core      |

| 0xA4      | Initialize typematic rate                                                                                                                                                                                                                            | LBT   | Core      |

| 0xDB      | StrongROM Test                                                                                                                                                                                                                                       | LBT   | Core      |

| 0xE2      | OEM security key test                                                                                                                                                                                                                                | LBT   | Core      |

| 0xC2      | Write PEM errors.                                                                                                                                                                                                                                    | LBT   | Core      |

| 0xBA      | Initialize the SMBIOS header and sub-structures.                                                                                                                                                                                                     | LBT   | Core      |

| 0xC3      | Display PEM errors.                                                                                                                                                                                                                                  | LBT   | Core      |

| 0xA8      | Overwrite the "Press F2 for Setup" prompt with spaces, erasing it from the screen.                                                                                                                                                                   | LBT   | Core      |

| 0xAA      | Scan the key buffer to see if the F2 key was struck after keyboard interrupts were enabled. If an F2 keystroke is found, set a flag.                                                                                                                 | LBT   | Core      |

| 0xE1      | Start Periodic Timer (TC Subscribe)                                                                                                                                                                                                                  | LBT   | Core      |

| 0xAC      | Check if "Enter SETUP" is pressed.                                                                                                                                                                                                                   | LBT   | Core      |

| 0x8F      | Count the number of ATA drives in the system and update the number in bdaFdiskcount.                                                                                                                                                                 | LBT   | Core      |

| 0x91      | Configure the local bus IDE timing register based on the drives attached to it.                                                                                                                                                                      | LBT   | Core      |

| 0x9F      | Check the total number of Fast Disks (ATA and SCSI) and update the bdaFdiskCount.                                                                                                                                                                    | LBT   | Core      |

| 0xD7      | Check if FirstWare HPA exists                                                                                                                                                                                                                        | LBT   | Core      |

| 0xAE      | Clear ConfigFailedBit and InPostBit in CMOS.                                                                                                                                                                                                         | LBT   | Core      |

| 0xB0      | Check for errors and decide if needs to run Setup.                                                                                                                                                                                                   | LBT   | Core      |

| 0xB2      | Change status bits in CMOS and/or the TrustedCore data area to reflect the fact that POST is complete.                                                                                                                                               | LBT   | Core      |

| 0xB5      | Fade out OEM Logo or post string                                                                                                                                                                                                                     | LBT   | Core      |

| 0xC5      | End hotkey detection (Server BIOS)                                                                                                                                                                                                                   | LBT   | Core      |

| 0xBE      | If BCP option is enabled, clear the screen before booting.                                                                                                                                                                                           | LBT   | Core      |

| 0xB6      | If password on boot is enabled, a call is made to Setup to check password. If the user does not enter a valid password, Setup does not return.                                                                                                       | LBT   | Core      |

| 0xBC      | Clear parity-error latch                                                                                                                                                                                                                             | LBT   | Core      |

|           | <u> </u>                                                                                                                                                                                                                                             | 1     | 1         |

- 이 문서는 삼성전자의 기술 자산으로 승인자만이 사용할 수 있습니다 -

- This Document can not be used without Samsung's authorization -

| POST Code | Function                                                                                       | Phase      | Component |

|-----------|------------------------------------------------------------------------------------------------|------------|-----------|

| 0xB7      | Initialize ACPI BIOS.                                                                          | LBT        | Core      |

| 0x9B      | Enable CPU management (Geyserville I)                                                          | LBT        | Core      |

| 0xBD      | Display Boot First menu if MultiBoot is installed and hotkey pressed.                          | LBT        | Core      |

| 0xBF      | Check virus and backup reminders.                                                              | LBT        | Core      |

| 0x97      | Create pointer to MP table in Extended BDA.                                                    | LBT        | Core      |

| 0x99      | Check support status for Self-Monitoring Analysis Reporting Technology (disk-failure warning). | LBT        | Core      |

| 0xB1      | Unload ROM Pilot                                                                               | LBT        | Core      |

| 0xDD      | Perform remote flash if requested                                                              | LBT        | Core      |

| 0xC7      | If UCR redirection is installed, remove display manager and unhook INT10                       | LBT        | Core      |

| 0XDF      | Shutdown the PXE UNDI code                                                                     | LBT        | Core      |

| 0xB3      | Store enhanced CMOS values in non-volatile area                                                | LBT        | Core      |

| 0xE4      | Last Legacy BIOS Task before hand off to UEFI/DXE                                              | LBT        | Core      |

| 0xB9      | Clear all screen graphics before booting.                                                      | bootLegacy | Core      |

| 0xC0      | INT19 entry for legacy boot                                                                    | bootLegacy | Core      |

| 0xEF      | Invalid AP #                                                                                   | SDXE       | Core      |

| 0xEF      | Non-Yohna and non-Morem class CPU found for SDXE (getTSCFreq)                                  | SDXE       | Core      |

| 0xEE      | AP cannot synch BSP in SDXE (syncWithBSP)                                                      | SDXE       | Core      |

| 0xEE      | BSP cannot synch w/ AP in SDXE (syncWithAP)                                                    | SDXE       | Core      |

- 이 문서는 삼성전자의 기술 자산으로 승인자만이 사용할 수 있습니다 -

- This Document can not be used without Samsung's authorization -

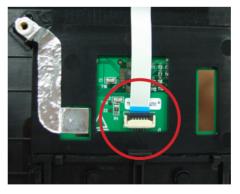

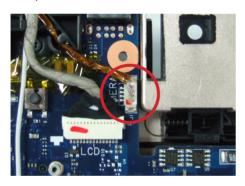

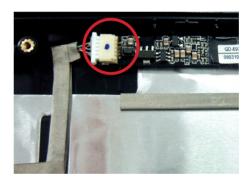

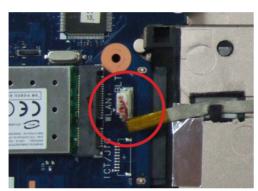

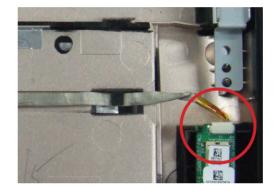

### **System Diagnostics Card**

• Connect debug card cable to J4 in Main board like picture.

• Debug code is shown at the viewer in red line.

- 이 문서는 삼성전자의 기술 자산으로 승인자만이 사용할 수 있습니다 -

- This Document can not be used without Samsung's authorization -

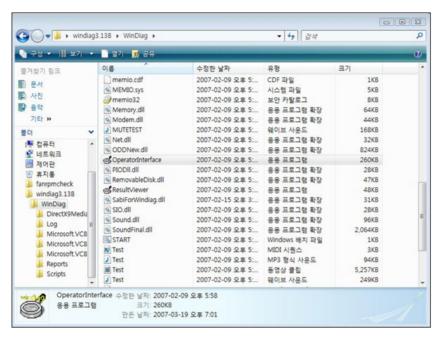

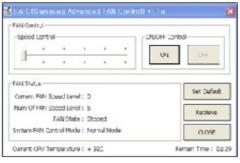

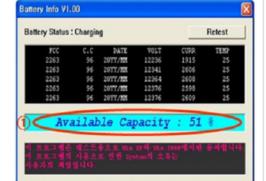

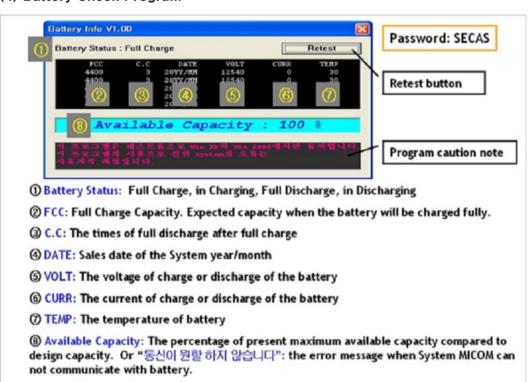

### 4-4. Diagnosis application

1. After copying Windiag3 in any folder, execute OperatorInterface.exe.

2. If OperatorInterface.exe runs properly, this window will be shown.

**(**

- 이 문서는 삼성전자의 기술 자산으로 승인자만이 사용할 수 있습니다 -

- This Document can not be used without Samsung's authorization -

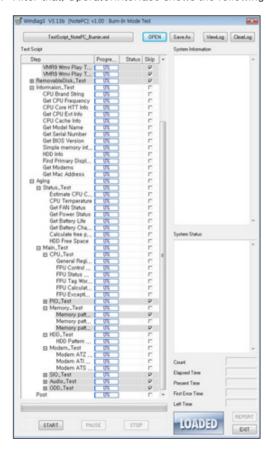

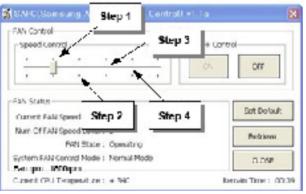

3. Click "Open" to open Script file.

In case of Note PC, click TestScrip\_NotePC\_Bumin.xml.

In case of Desktop, click의 TestScript\_Desktop\_Burnin.xml

When you would like to execute each item for only once: Select the testScriptFormat\_Concurrent.xml.

4. After that, OperatorInterface shows the following scripts on the left of the display.

- 이 문서는 삼성전자의 기술 자산으로 승인자만이 사용할 수 있습니다 -

- This Document can not be used without Samsung's authorization -

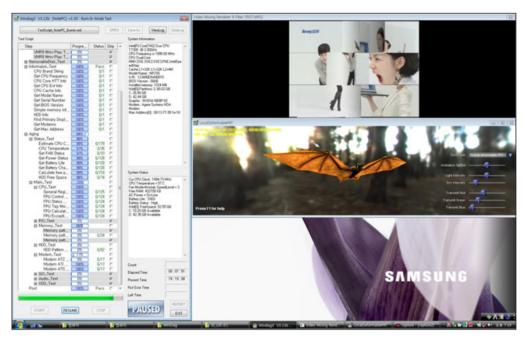

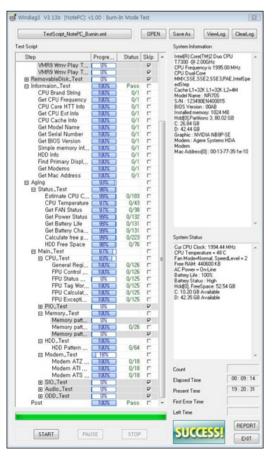

5. Click "Start" button, then test begins.

6. If you want to stop this, click "stop" button. If all modules don 't stop in 2 minutes 30 seconds, message window will ask you about a forced stop. At that time, by selecting "yes", it can be ended by force.

7. Click "EXIT", then it will be closed.

- 이 문서는 삼성전자의 기술 자산으로 승인자만이 사용할 수 있습니다 -

- This Document can not be used without Samsung's authorization -

### 4-5. Hardware Troubleshooting

For information on how to disassemble the parts, refer to the "Disassembly and Reassembly" section of Chapter 4.

#### LCD related troubles.

- 1. The screen is dark or the colors of the screen are distorted.

- Check the connection status between the LCD module and the LCD cable, between the LCD cable and the main board LCD connector and between the LCD cable and the LCD inverter.

- Replace the LCD cable or LCD inverter.

- Check if there is a part of the LCD that is bent or broken due to impact.

- 2. No picture appears on the screen.

- Check the connection status between the LCD module and the LCD cable, between the LCD cable and the main board LCD connector and between the LCD cable and the LCD inverter.

- Replace the LCD cable or LCD inverter.

- Check if the System LED of the main board is blinking. (Check if it is operating or not)

- Check if the memory module is out of order.

- Check if the Power button can be normally pressed.

- 3. The LCD brightness is not adjusted.

- Check if the LCD inverter is out of order.

- Check the BIOS version and check if the standard adapter is used.

- Replace the LCD cable or LCD inverter and check if it is out of order.

- 4. The LCD blinks while the system is in operation.

- Check if there is a magnetic body near the LCD connector or the system or check if there is an exterior defect to the LCD or system.

- Replace the LCD cable or LCD inverter and check if it is out of order.

- Check if a standard adapter is being used (19V/4.73A/90W).

- 이 문서는 삼성전자의 기술 자산으로 승인자만이 사용할 수 있습니다 -

- This Document can not be used without Samsung's authorization -

### **Main System Troubles**

- 5. The system is not turned on.

- Check if the AC adapter LED is lit and if the adapter is properly connected to the system. (Check the adapter LED)

- If the AC adapter is not connected, check the charge status of the battery. Even if the battery is charged, if the remaining battery charge is too low, the system may not be turned on.(As the following figure shows, press the PUSH button on the battery and check the remaining battery charge via the LEDs)

- Check if there are any alien substances in the Power switch.

- Replace the main board.

- 6. Although system power is supplied, the system does not boot or immediately turns off after being turned on.

- Since this may be a short circuit in the system, disconnect the power immediately, disassemble the system and check if there are any conducting alien objects such as a screw inside.

- Check the connection status between the CPU and the RHE.

- Replace the memory module and check if it is out of order.

- Reset the RTC Reset terminal next to the memory socket.

- Replace the main board.

- 7. The PCMCIA card is not inserted or the Eject button does not work.

- This may occur when the insulator within the PCMCIA slot is enwrapped.

- Replace the PCMCIA slot frame and check if it is out of order.

- 8. There is no sound from the speaker.

- Check if the sound is muted after booting up Windows.

- Control panel → Sound, Check if the default output is "Speaker".

- Check the connection status of the speaker cable and check if the speaker is out of order.

- Check if there is a magnetic object near the speaker.

- Replace the main board.

- 이 문서는 삼성전자의 기술 자산으로 승인자만이 사용할 수 있습니다 -

- This Document can not be used without Samsung's authorization -

- 9. I cannot hear sound through the headphones.

- Check if the sound is muted in Windows.

- Check that the default setting is "Speaker" on Control Panel-Sound-Playback.

- Turn the volume up.

- Check a foreign substance in Headphone jack.

- Replace the main boarda.

- 10. Internal MIC or External MIC isn't work.

- Check the sound driver and setting.

Like below picture, Check if the default record device is "MIC" at the Control panel → Sound.

- In case of Internal MIC, Check the MIC connection.

- Replace the main boarda.

- 11. HDMI port isn't work correctly.

- Check if Audio and Video driver is installed correctly.

- Check if Display Manager is installed correctly.

- If only sound isn't out, Check the default output device is "HDMI" on Sound information.

- Change Main board.

- The sound dose not work with DVI-HDMI cable, Please use the HDMI to HDMI Cable.

- 이 문서는 삼성전자의 기술 자산으로 승인자만이 사용할 수 있습니다 -

- This Document can not be used without Samsung's authorization -

#### 12. The HDD is not recognized.

- Check if HDD connection is no problem.

- If the 'Operating system not found' message appears during the booting process even though the HDD is recognized by CMOS, the operating system of the HDD may be corrupted or the HDD is out of order. In this case, format the HDD and reinstall the operating system or replace the HDD with a new one.

#### 13. Touch Screen is work abnormally.

- Check the connection of Touch Screen FFC.

- Check the connection of Touch Pad Module.

- If you can not find any connection issue, please change the part.

- 이 문서는 삼성전자의 기술 자산으로 승인자만이 사용할 수 있습니다 -

- This Document can not be used without Samsung's authorization -

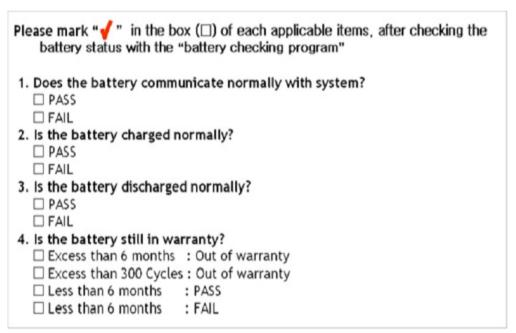

- 14. The battery is not charge or the battery charge LED malfuctions.

- Check the standard voltage of the adapter.

- Check if the battery is defective.

- Replace the Main board.

- 15. Camera is not working correctly

- Check if the Camera cable connection is no problem on Main board.

- Check if connection is no problem between Camera cable and Camera module.

- Change the Camera cable or the Camera module.

- Replace the Main board.

- 16. The LAN function does not work.

- Check if the LAN cable is properly connected.

- Check of the LAN driver is properly installed.

- If the driver is properly installed, check if the LAN cable jack is out of order.

- Replace the Main Board.

- 17. The wireless LAN does not work normally.

- Check if the WLAN driver is properly installed.

- Check if the WLAN antenna cable is properly connected.

- Change WLAN card and check it.

- Replace the Main Board.

- \*. In the case of Intel Shirley Peak 1x2 AGN, Atheros 802.11 BG card there are the #1, #2 antenna pin, In the case of Intel Shirley Peak 3x3 AGN card there are all of #1, #2, #3 pin.

- 이 문서는 삼성전자의 기술 자산으로 승인자만이 사용할 수 있습니다 -

- This Document can not be used without Samsung's authorization -

- 18. Bluetooth isn't work normally.

- Check the connection between Main board and Bluetooth cable.

- Check the connection between Bluetooth module and Bluetooth cable.

### When Bbooting up the Computer

- 19. The "Invalid system Disk, Replace the Disk and then press any key" message appears.

- This message may appear when the connected USB memory or CD medoa does not include bootable data.

- The "Reboot and Select proper Boot device or Insert Boot Media in selected Boot device and press a key" message appears.

- Check if the signal and power cables are properly connected to the hard disk drive.

- Check if the hard disk drive is recognized in the BIOS SETUP.

- The operating system on the hard disk drive is corrupted. Reinstall Windows.

- 20. The "To enter BIOS SETUP, press <F2>, To continue, press <F1>" message appears.

- This message happen when the BIOS settings are different from the system environment. In this case, setup the BIOS according to your system environment.

- Press <F2> to enter the BIOS SETUP.

- Check if the data and time are correct in the BIOS SETUP.

- Save the settings and restart the system.

- 21. The "CMOS Checksum error" message appears.

- This message may appear when the CMOS battery of the main board is completely discharged.

In this case, replace the battery with a new one of the same type and set up the BIOS SETUP according to your system environment.

- 22. Windows boots up in safe mode.

- This may happen when Windows was not shut down normally.

Therefore, shut down the system by selecting Start > Turn Off Computer.

- This may happen when the system settings have been incompletely recognized.

- Run Check Disk.

- 이 문서는 삼성전자의 기술 자산으로 승인자만이 사용할 수 있습니다 -

- This Document can not be used without Samsung's authorization -

- 23. I cannot boot up the computer with a USB floppy drive or from USB memory.

- Check if the diskette is bootable.

- This may happen when the booting priority of the device is low. In this case, change the booting priority in the BIOS SETUP.

### When Shutting Down the Computer

- 24. The computer is not shut down.

- If Windows does not end normally, you can forcibly shut down the system by pressing the Power button.

If the power saving feature is activated on the Power button, press the Power button for more than 4 seconds to turn the computer off. If the computer is then turned on again, Check Disk is automatically run.

#### Windows / Screen Related Problem

- 25. The computer hangs while running a program

- If the running program causes an error.

- In Windows, press the <Ctrl>, <Alt> and <Del> key combination, select the application program and click on End Task in the Applications tab of the [Windows Task Manager] window.

- If Windows does not respond, restart the computer. Restart the computer by pressing the Power button.

- 26. No picture is displayed on the external monitor.